Keysight stellt Chiplet PHY Designer für die Simulation von D2D PHY IP mit Unterstützung des UCIe™-Standards vor

Nutzt die Technologie von Keysight EDA und die Erfahrung bei der Simulation komplexer Bitübertragungsschichten von SerDes und Speichern.

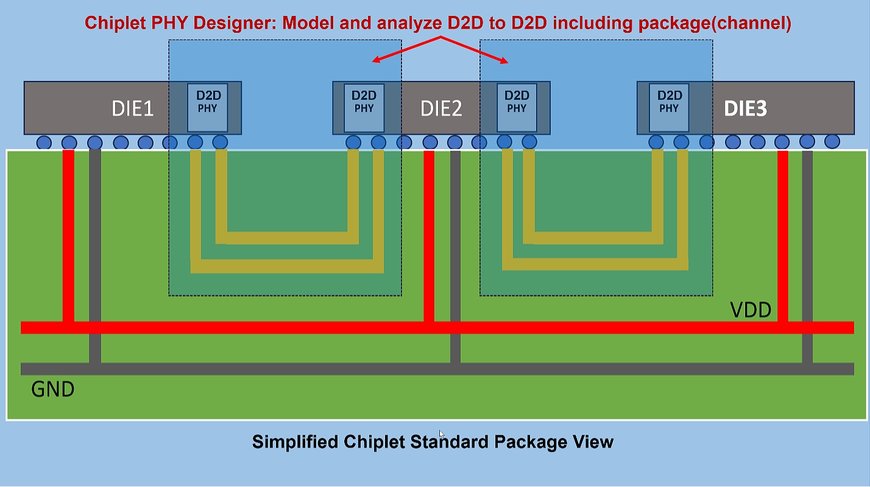

Der Chiplet PHY Designer simuliert die UCIe-Spezifikation für die Bitübertragungsschicht von D2D-Verbindungen.

Keysight Technologies stellt Chiplet PHY Designer vor, das jüngste Mitglied seiner Familie digitaler Hochgeschwindigkeits-Design- und -Simulations-Tools, das die Simulation von Die-to-Die (D2D)-Verbindungen ermöglicht. Das ist ein wichtiger Schritt bei der Verifizierung der Leistung von heterogenen und 3D-IC-Designs, die allgemein als Chiplets bezeichnet werden. Das neue EDA-Tool (Electronic Design Automation) ist das branchenweit erste Tool, das detaillierte Modellierungs- und Simulationsfunktionen bietet, mit denen Entwickler von Chiplets schnell und präzise überprüfen können, ob ihre Designs die Spezifikationen des UCIe™-Standards (Universal Chiplet Interconnect Express™) erfüllen.

UCIe entwickelt sich zur führenden Chiplet-Verbindungsspezifikation in der Halbleiterindustrie. Es handelt sich dabei um einen offenen Standard, der die Verbindung zwischen Chiplets in einem modernen 2,5D- oder 3D-Gehäuse definiert. UCIe wird derzeit von vielen der führenden Anbieter von Halbleitertechnik und EDA-Tools sowie von Foundries und Chiplet-Entwicklern unterstützt oder übernommen. Entwickler, die den Interconnect-Standard verwenden und sicherstellen, dass ihre Chiplets den Spezifikationen entsprechen, tragen zum Aufbau eines breiten Ökosystems für die Interoperabilität und den Handel mit Chiplets bei.

Das Forschungs- und Entwicklungsteam von Keysight EDA arbeitet seit Jahrzehnten an der Modellierung und Simulation von digitalen Hochgeschwindigkeitsschnittstellen, die mit den Spezifikationen der Industrie übereinstimmen. Beispielsweise bietet ADS Memory Designer mit seinem IBIS-AMI-Modellierer eine umfassende Abdeckung von Speicherschnittstellen wie GDDR7, DDR5, LPDDR5 und HBM3. Die strenge und konforme JEDEC-Testlösung verarbeitet über 100 Test-IDs mit dem gleichen Testalgorithmus wie die Keysight Infinium-Oszilloskopfamilie.

Der Simulator für die Bitübertragungsschicht des Chiplet PHY Designers zeichnet sich durch folgende Merkmale aus:

- Unterstützung des UCIe-Standards für die Bitübertragungsschicht – automatisches Parsing von Signalen gemäß den Standard-Namenskonventionen, automatisierte Verbindungen zwischen mehreren Dies durch Package-Interconnects, standardgesteuerte Simulationsansteuerung, wie z. B. Geschwindigkeitsgrad, und intuitive Messansteuerung durch eine spezielle Tastkopfkomponente.

- Messung der Spannungsübertragungsfunktion (Voltage Transfer Function, VTF) – Präzise Berechnung der VTF, um die Einhaltung der UCIe-Spezifikation zu gewährleisten, und Analyse der System-Bitfehlerrate (BER) bis auf 1e-27 oder 1e-32. Misst Augendiagrammhöhe, Augenbreite, Versatz, Maskenrand und BER-Kontur.

- Analyse der vorwärts gerichteten Taktung zur genauen Erfassung des asynchronen Taktverhaltens.

Weitere Informationen unter Chiplet PHY Designer.

www.keysight.com

Fordern Sie weitere Informationen an…