elektronik-news.com

27

'22

Written on Modified on

Mouser News

Die quelloffene, lizenzfreie und erweiterbare Befehlssatzarchitektur RISC-V gewinnt in der Branche an Dynamik

Langer Teaser: Damit änderte sich die Art und Weise der Prozessorenentwicklung bei den führenden Anbietern dieser Ära schlagartig.

Neue Befehlssatzarchitekturen (ISA) werden in der Halbleiterindustrie nicht sehr häufig eingeführt. Bei der letzten bedeutenden Veränderung entwickelte das Unternehmen Arm Kerne und vertrieb sie als lizenzierte IP (geistiges Eigentum).

Und jetzt, in einer Zeit von Handelskriegen und einer Pandemie, erweist sich die Verfügbarkeit eines quelloffenen, lizenzgebührenfreien, erweiterbaren ISA als transformative und disruptive Kraft.

Kurzer Teaser: Befehlssatzarchitekturen haben sich in den letzten vierzig Jahren kaum verändert, aber der quelloffene, lizenzgebührenfreie, erweiterbare RISC-V bringt frischen Wind in die Branche.

SEO-Schlüsselwörter: x86, MIPS, ISA, Befehlssatzarchitektur, RISC, CISC, RISC-V, Microchip, AVR, Atmel, Atmel AVR, Arm, Intel, SoC, FPGA, SparkFun, SEEED

Die Prozessor-Befehlssatzarchitektur hat sich in 40 Jahren kaum verändert

Über Jahrzehnte haben Intel und Arm die Prozessorarchitekturen dominiert. Intel und seine x86-Architektur beherrschen den Bereich der Computer-Workstations, Desktops und Server. Gleichzeitig hat Arm einen breiten Markt mit IoT-Geräten, Unterhaltungselektronik und industriellen Automatisierungssystemen aufgebaut. Andere Embedded-Prozessor- und Mikrocontroller-Architekturen wie der AVR von Atmel und der PIC/MIPS von Microchip haben ihre Nische gefunden, aber nicht die gleiche Größe wie die dominierenden Anbieter erreicht. Das IP-Lizenzierungsmodell von Arm wurde von den meisten MCU- und MPU-Anbietern im Embedded-Bereich weitgehend übernommen.

Es zeichnet sich jedoch eine revolutionäre Veränderung ab, die sich schnell durchsetzt und die bestehenden Normen auf dem Prozessormarkt in Frage stellt. Führende Anbieter setzen die quelloffene RISC-V-Befehlssatzarchitektur (ISA) zunehmend ein, da die Kunden die kommerziellen und technologischen Vorteile eines quelloffenen Ansatzes zu schätzen wissen. In diesem Beitrag beschreiben wir die Entstehung von RISC-V und heben einige der Faktoren hervor, die diese Architektur attraktiv machen. Wir führen Produktbeispiele an und konzentrieren uns dabei auf Evaluierungsboards, Entwicklungsressourcen und das wachsende Ökosystem von Software-Toolchains.

Die Befehlssatzarchitektur (ISA) als eigentliche Verbindung zwischen Prozessorhardware und Software

Eine Befehlssatzarchitektur (ISA) bildet die Schnittstelle zwischen der Welt der Software und der Prozessorhardware. Die ISA definiert jeden einzelnen Teilaspekt, wie ein Programm mit der verfügbaren Hardware interagiert, einschließlich der Rechenlogik (ALU), der Register, des Speichers und der Steuerlogik. Sie legt auch die Datenwortbreiten, die unterstützten Datentypen und die Adressierung von Registern und Speicherplätzen fest. Kurz gesagt, ein ISA ist eine Zusammenfassung eines Prozessors.

Es gibt viele verschiedene ISA-Typen, aber für die meisten praktischen Zwecke sind die beiden wichtigsten Architekturtypen die CISC (Complex Instruction Set Computer, komplexer Befehlssatz) und die RISC (Reduced Instruction Set Computer, reduzierter Befehlssatz). Wie der Name schon sagt, enthält ein CISC-Prozessor viele komplexe und spezialisierte Befehle für verschiedene Anwendungen, von denen einige eventuell nur selten zum Einsatz kommen. Ein CISC-Prozessor bietet außerdem viele verschiedene Adressierungsmöglichkeiten und verwendet Befehle mit variabler Länge. CISC-basierte Prozessoren sind teuer in der Entwicklung, erfordern anspruchsvollere Software und Programmiertools und benötigen deutlich mehr Zeit für die Entwicklung. Ein Beispiel für einen CISC-ISA ist der Intel x86.

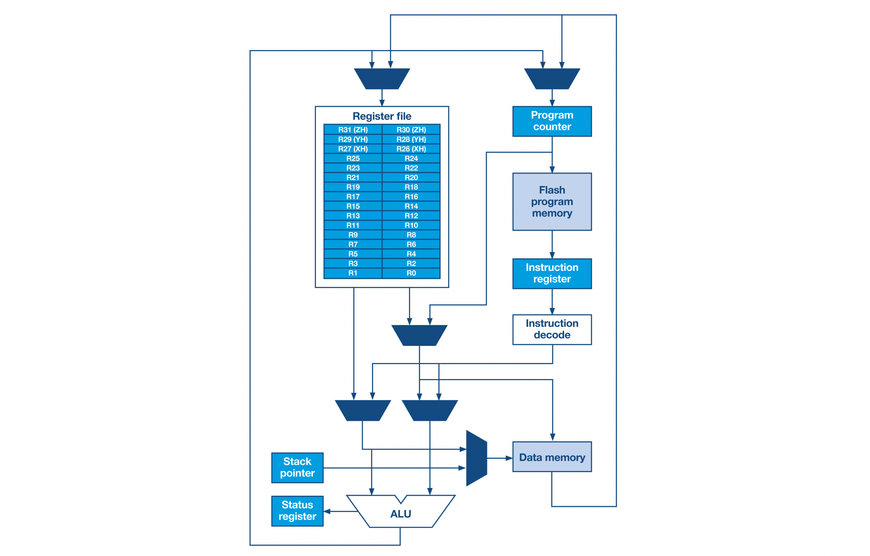

Im Gegensatz dazu ist ein RISC-basierter Prozessor wesentlich einfacher aufgebaut und verfügt über eine begrenzte Anzahl häufig verwendeter Befehle, einige wenige verschiedene Adressierungsmodi und eine feste Befehlslänge. Durch den Einsatz von Befehlspipelining-Techniken ist ein schnellerer Verarbeitungsdurchsatz möglich. Im Gegensatz zu einem CISC-Prozessor, bei dem Operanden (Datenwerte) in den Speicher verschoben werden, um Berechnungen durchzuführen, verwendet ein RISC-Prozessor interne Register. Beispiele für einen RISC-basierten ISA sind Arm, AVR, PIC und MIPS.

Beispiel für die RISC-Architektur eines Microchip AVR-Mikrocontrollers.

ISAs – Welche sind die entscheidenden Erfolgsfaktoren?

Im weiteren Verlauf dieses Beitrags befassen wir uns nur noch mit RISC-basierten Prozessoren. Wenn wir von einem Prozessor sprechen, meinen wir damit ein beliebiges Verarbeitungssystem, wie z. B. Mikrocontroller und Mikroprozessoren. Gängige RISC-ISAs sind mit 8-, 16- und 32-Bit-Datenwortbreiten erhältlich, wobei 64-Bit- und 128-Bit-ISAs in der Regel für anspruchsvollere und spezielle Anwendungen eingesetzt werden. Die Wortbreite hat einen erheblichen Einfluss auf das Hardwaredesign, die Geschwindigkeit, mit der der Prozessor arbeiten kann, sowie die verfügbare Speichergröße.

Ein ISA muss mindestens eine arithmetische Logikeinheit, einen Speicher und eine Steuerlogik enthalten. Die Rechenlogik (ALU) führt grundlegende Berechnungsfunktionen wie Addieren, Vergleichen und Subtrahieren unter Verwendung von Registern oder unmittelbar in sich selbst aus. Dabei kann die Speicheradressierung absolut oder indiziert sein. Die Steuerlogik führt bedingte und unbedingte Verzweigungen und andere Adressierungsaufgaben aus.

Der Befehlssatz eines ISA besteht aus Opcodes (Maschinencode), mit denen die auszuführende Aufgabe, in der Regel für einen oder mehrere Operanden, festgelegt wird. Im Atmel/Microchip AVR ISA definiert ADC beispielsweise die Addition von Operanden in zwei Registern mit einem Carry-Flag und legt das Ergebnis im Zielregister ab. In der ISA-Dokumentation ist angegeben, wie viele Taktzyklen oder Programmzähler-Iterationen jede Anweisung benötigt. In einem RISC-Prozessor werden die meisten Befehle in einem Zyklus ausgeführt.

Für die Hersteller von Mikrocontrollern (MCUs) und Mikroprozessoren (MPUs) ist die Entwicklung einer ISA ein zentraler Bestandteil der Produktentwicklung. Dadurch sind ISAs zu proprietären Systemen geworden, die für eine bestimmte Serie von Geräten entwickelt wurden. Beispiele hierfür sind der Atmel/Microchip AVR (8, 16, 32-bit), der Microchip PIC (8, 16, 32-bit) und MIPS (32, 64-bit).

Das Unternehmen Advanced RISC Machines (Arm) wurde Anfang der 1990er Jahre als Spin-off von Acorn gegründet und brach mit dem traditionellen MCU/MPU-Geschäftsmodell. Arm wählte den Weg der Lizenzierung von geistigem Eigentum und erzielte seine Einnahmen aus Lizenzgebühren, anstatt selbst Geräte zu produzieren und zu verkaufen. Das Modell von Arm setzte sich schnell durch und befreite die Halbleiterhersteller von der Aufgabe, ihre ISA zu entwickeln und zu portieren. Heute bieten die meisten Halbleiterhersteller Prozessoren an, die auf dem Arm-ISA basieren. Einige bieten auch darüber hinaus Produkte an, die auf dem Arm-ISA basieren. Jeder Hersteller zahlt für jedes verkaufte Gerät eine Lizenzgebühr an Arm. Arm kontrolliert den Lebenszyklus und die fortlaufende Entwicklung der ISA.

Die einzelnen ISAs haben natürlich ihre Vor- und Nachteile, aber der Erfolg einer bestimmten Prozessorarchitektur hängt nicht nur von ihren technischen Merkmalen ab, sondern auch von der Verfügbarkeit eines Ökosystems von Entwicklungs-Tools für die Softwareentwicklung. Toolchains, integrierte Entwicklungsumgebungen (IDEs), Compiler, Debugger und anwendungsspezifische Middleware spielen eine entscheidende Rolle für die zunehmende Verbreitung eines Prozessors und seines ISAs.

Befehlssatzarchitektur als Open-Sourcing

Für die Halbleiterhersteller stellte Arm eine Standard-ISA zur Verfügung, auf deren Grundlage sie die Peripherieschnittstellen des Geräts anpassen und verbessern konnten, um sie an spezifische Anwendungen anzupassen. Dieses Konzept ermöglichte eine gewisse Produktdifferenzierung gegenüber anderen Halbleiterherstellern, die ebenfalls IP von Arm verwenden. Für die etablierten ISAs wie AVR, PIC usw. hat die breite Akzeptanz von Arm ihre Reichweite auf dem Markt insgesamt verringert.

Für Prozessorkunden ist die Entscheidung für eine Arm-ISA jedoch eine sinnvolle Entscheidung, denn es gibt mehrere Prozessoranbieter. Das erleichtert die Auswahl an Kaufoptionen für das Second Sourcing ähnlicher Teile. Die Standardisierung der Entwicklung rund um eine bestimmte Toolchain ist auch kommerziell sinnvoll.

In einer Branche, in der viele Open-Source-Konzepte umgesetzt wurden, war der Bereich der Prozessor-Befehlssatzarchitekturen sehr proprietär. Zumindest bis zum Erscheinen des RISC-V-ISA im Jahr 2010. Der ISA wurde ursprünglich an der University of California in Berkeley für akademische Zwecke entwickelt und das Konzept der Open-Source-Entwicklung setzte sich schnell durch. Der Hintergrund für die Open-Source-Entwicklung war die Überlegung, dass sich das ISA-Design in den letzten vierzig Jahren kaum verändert hatte. Die Offenlegung als Open Source sollte die Interaktion und die Wiederverwendung von Software fördern und damit die langfristige Unterstützung durch die Toolchain-Lieferanten der Hersteller gewinnen. Da es sich um einen Open-Source-ISA handelt, müssen Hersteller keine Lizenzgebühren zahlen und dürfen neue Anweisungen und Erweiterungen entwickeln.

Die Basis des RISC-V-ISA und die zugehörigen Erweiterungen werden im Rahmen einer Zusammenarbeit zwischen der akademischen Forschungsgemeinschaft und der Industrie entwickelt und verwaltet. Der RISC-V-ISA unterstützt 32-, 64- und 128-Bit-Datenwortbreiten.

Im Jahr 2015 machte die Entwicklung von RISC-V einen bedeutenden Schritt nach vorn, als durch einen Zusammenschluss von Halbleiterunternehmen die RISC-V Foundation gegründet wurde. Die Vorteile der Lizenzgebührenfreiheit und der Erweiterbarkeit haben die Aufmerksamkeit der Hersteller geweckt. Arm-Lizenznehmer können den Befehlssatz nicht an bestimmte Anwendungen anpassen, z.B. an einen niedrigen Stromverbrauch – RISC-V-Lizenznehmer können das hingegen schon. Die RISC-V Foundation hat branchenweit mittlerweile mehr als 750 Mitglieder.

Da viele große Prozessorhersteller ihr Interesse an RISC-V zeigten, wollte auch die Software-Tool-Community nicht den Anschluss verlieren und begann, ihre IDEs und Toolchains um Unterstützung für RISC-V zu erweitern.

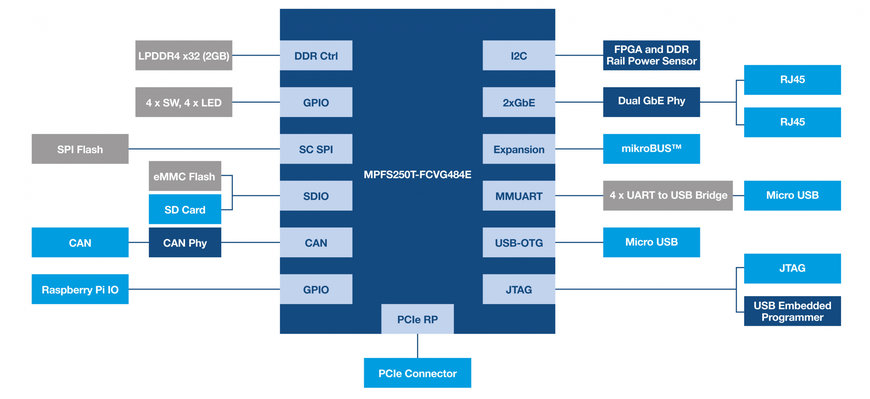

Funktionelles Blockdiagramm des Microchip RISC-V PolarFire SoC Evaluierungskits.

Erste Schritte mit RISC-V

Einer der ersten verfügbaren RISC-V-basierten 32-Bit-Prozessoren war der SiFive Freedom E31 SoC. Das Unternehmen SiFive wurde von den Entwicklern der RISC-V-ISA gegründet, die ihr Know-how schnell auf den Markt bringen wollten. Um das Prototyping zu beschleunigen, finanzierte SiFive per Crowdfunding ein kostengünstiges Development Board im Arduino-Format, das HiFive1. Das SiFive HiFive1 B bietet Wi-Fi-Konnektivität und 32 MB Flash-Speicher.

SEEED bietet ebenfalls ein Development Board im Feather/MKR-Format an, das Sipeed Longan Nano. Es verfügt über ein 0,96-Zoll-LCD und arbeitet mit einem GigaDevice 32-Bit-RISC-V-Kern.

SparkFun hat ein Development Board im Angebot, das dem HiFive1 B ähnelt. Das RED-V RedBoard von SparkFun verwendet ebenfalls den Arduino UNO-R3 Formfaktor und den SiFive E310 RISC-V SoC.

Das PolarFire SoC FPGA Icicle Development Board von Microchip ist eine komplexere RISC-V Plattform, die sich an professionelle Entwickler richtet.

Das PolarFire SoC wurde als Evaluierungsplattform für den Linux-fähigen RISC-V RV64-Kern mit fünf Kernen entwickelt und verfügt außerdem über 256k Logikelemente und einen Rechenblock mit 784 Einheiten. Das Icicle-Kit eignet sich ideal für das Prototyping von Echtzeit-Designs mit geringem Stromverbrauch, von IoT-Sensoren bis hin zu Machine Learning-Anwendungen und bietet umfassende Schnittstellen für Peripheriegeräte, darunter HDMI, PCIe, USB, CAN, SPI und I2C. Optional sind externe Erweiterungsschnittstellen wie eine mikroBUS-Buchse und ein 40-poliger Raspberry Pi-Anschluss verfügbar.

Die weitere Entwicklung von RISC-V

In relativ kurzer Zeit hat die RISC-V-Befehlssatzarchitektur erheblich an Dynamik gewonnen. Die Foundation feierte im Juli 2020 ihr zehnjähriges Jubiläum der ersten RISC-V-Entwicklung. Laut der Website der Foundation sind inzwischen 12 RISC-V-basierte SoCs und 86 Cores auf dem Markt erhältlich.

RISC-V hat sich schnell als praktikable, erweiterbare und lizenzgebührenfreie Alternative zu anderen ISAs etabliert.

www.mouser.com

Fordern Sie weitere Informationen an…